Accumulateur ou registre A dans le microprocesseur 8085

Le registre A est un registre de 8 bits utilisé dans le 8085 pour effectuer des opérations arithmétiques, logiques, E/S & LOAD/STORE. Le registre A est assez souvent appelé comme un accumulateur. Un accumulateur est un registre pour le stockage intermédiaire à court terme des données arithmétiques et logiques dans l’unité centrale de traitement d’un ordinateur.Dans une opération arithmétique impliquant deux opérandes, un opérande doit être dans ce registre. Et le résultat de l’opération arithmétique sera stocké ou accumulé dans ce registre. De même, dans une opération logique impliquant deux opérandes, un opérande doit se trouver dans l’accumulateur. De même, certaines autres opérations, comme la complémentation et l’ajustement décimal, ne peuvent être effectuées que sur l’accumulateur.

Envisageons maintenant un segment de programme qui implique le contenu d’Accumuler seulement. Dans le jeu d’instructions 8085, STA est un mnémonique qui signifie STore Accumulator contents in memory. Dans cette instruction, le contenu de 8 bits de l’accumulateur sera stocké dans un emplacement mémoire dont l’adresse de 16 bits est indiquée dans l’instruction comme a16. Cette instruction utilise l’adressage absolu pour spécifier la destination. Cette instruction occupe 3 octets de mémoire. Le premier octet est nécessaire pour l’opcode, et les 2 octets successifs suivants fournissent l’adresse de 16 bits divisée en 8 bits chacun consécutivement.

| Mnémoniques, Opérande | Opcode (en HEX) | Octets |

|---|---|---|

| Adresse STA | 32 | 3 |

Considérons la STA 4050 A un exemple d’instruction de ce type. Il s’agit d’une instruction de 3 octets. Le premier octet contiendra la valeur hexagonale de l’opcode 32H. Comme dans le codage du langage d’assemblage 8085 supporte l’octet de bas ordre de l’adresse doit être mentionné en premier puis l’octet de haut ordre de l’adresse doit être mentionné ensuite. Ainsi, le prochain octet de la mémoire contiendra 50H et après cela, 40H sera conservé dans le dernier tiers de l’octet. Supposons que le contenu initial de l’accumulateur soit ABH et que le contenu initial de l’emplacement mémoire 4050H soit CDH. Donc, après l’exécution, le contenu de l’accumulateur restera ABH et le contenu de l’emplacement 4050H deviendra ABH en remplaçant son contenu précédent CDH. Le traçage du contenu de cette instruction a été montré ci-dessous –

| Avant | Après | |

|---|---|---|

| . (A) | ABH | ABH |

| (4050H) | CDH | ABH |

| Adresse | Codes Hex | Mnémonique | Commentaire |

|---|---|---|---|

| 2008 | 2A | STA 4050H | Le contenu de l’emplacement mémoire 4050H ← A |

| 2009 | 50 | Octet d’ordre inférieur de l’adresse | |

| 200A | 40 | Octet d’ordre supérieur de l’adresse |

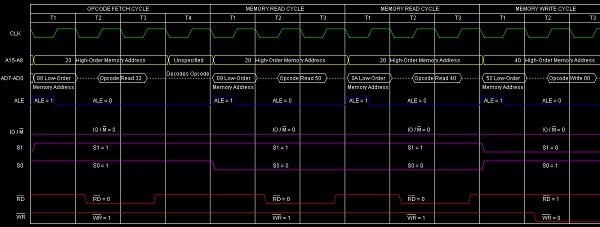

Le diagramme de synchronisation de cette instruction STA 4050H est le suivant .

Résumé – Ainsi cette instruction SDA 4050H nécessite 3 Octets, 4-Machine Cycles (Opcode Fetch, Memory Read, Memory Read, Memory Write) et 13 T-States pour son exécution comme le montre le diagramme de timing.

.